|

一文了解刻蚀、薄膜沉积和离子注入工艺

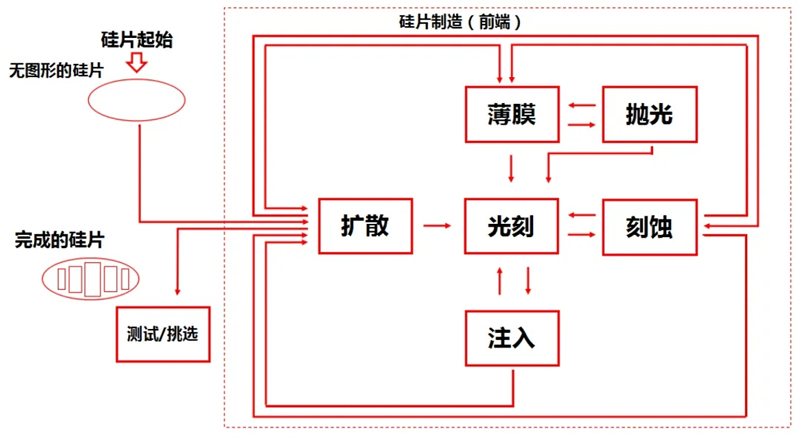

在集成电路制造流程中,前道工序(FEOL)是为了将芯片电路设计图从掩模转移到硅晶圆上,以实现预定的芯片功能。前道工序包括十余项工艺,主要有:扩散、氧化、涂胶、光刻、显影、刻蚀、离子注入、去胶、退火、薄膜沉积和抛光等。

扩散工艺是,通过分子热运动控制半导体中特定区域内杂质的类型、浓度和深度;氧化工艺是指在硅晶圆表面形成保护性氧化层;涂胶工艺是指在硅晶圆表面均匀涂覆光刻胶。

光刻工艺是,通过曝光将电路图转移至硅晶圆表面;显影工艺是指利用显影剂去除被曝光的光刻胶;刻蚀工艺是指通过离子撞击去除多余的膜层材料;离子注入工艺是将掺杂离子注入硅晶圆表面;去胶工艺则是去除硅晶圆表面的光刻胶。

退火工艺是,通过高温下的热处理激活掺杂离子,使其具有电活性,同时消除注入损伤;薄膜沉积工艺是指在硅晶圆表面添加如导电层、绝缘介质层等,实现器件互连以及芯片的多层结构;抛光工艺是指去除硅晶圆表面多余材料并实现表面平坦化。

一、“减法工艺”――刻蚀

刻蚀工艺是前道工序中重要的一环。刻蚀的基本原理是,利用化学或物理方法选择性的去除不必要材质的一个过程。刻蚀工是在镀膜、涂胶、光刻、显影之后,通过刻蚀将暴露在晶圆表面不必要的薄膜材质去除掉,留下所需的部分,然后再去除多余的光刻胶。多次重复上述步骤即可得到复杂构造的集成电路。因为是材料的去除,所以通常将刻蚀称为“减法工艺”。

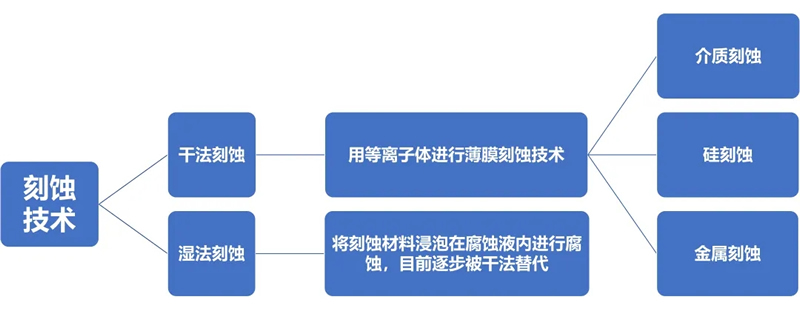

刻蚀的分类

根据工作原理不同,刻蚀通常分为干法刻蚀和湿法刻蚀。两者的主要区别在于使用等离子气体还是液体进行刻蚀,其中干法刻蚀的市场占比超过 95%。

干法刻蚀也称等离子刻蚀,是使用气态的化学刻蚀剂去除部分材料并形成可挥发性的生成物,然后将其抽离反应腔的过程。

等离子体刻蚀机根据等离子体产生和控制技术的不同分为两大类,即电容耦合等离子体(CCP)刻蚀机和电感耦合等离子体(ICP)刻蚀机。

CCP 刻蚀机主要用于电介质材料的刻蚀工艺,其刻蚀对象主要是,氧化硅、氮化硅、二氧化铪等介质材料。ICP 刻蚀机主要用于硅刻蚀和金属刻蚀,也被称为导体刻蚀机,其刻蚀对象包括硅材料(单晶硅、多晶硅和硅化物等)和金属材料(铝、钨等)。

湿法刻蚀是将晶圆浸入化学溶液中进行腐蚀去除。该方法具有成本低、刻蚀速度快和生产率高的优势。湿法刻蚀的缺点是,掩膜与刻蚀后的氧化膜不能完全对齐,因此难以保证制程线宽的精细度,会导致良率的下降。

此外,原子层刻蚀(ALE)将是下一代主流刻蚀技术。随着特征尺寸的不断缩小,原子层刻蚀能够精密控制被去除材料量而不影响其他部分,可以用于定向刻蚀。目前原子层刻蚀在芯片制造领域并没有取代传统的等离子刻蚀,而是被广泛用于原子级目标材料精密去除的过程。

如果说光刻机的精度决定了集成电路刻蚀的尺寸,那么刻蚀机的精度则决定了光刻的尺寸能否进行实际加工。两个环节同等重要,与制程和产品的良率息息相关。

二、“加法工艺”――薄膜沉积

集成电路是由一系列有源和无源电路元件(如晶体管、存储单元等)堆叠而成的 3D 结构,其中有很多用来实现结构之间互连的铝或铜金属层。同时为了保证各层金属之间绝缘,还需要在制造过程中利用沉积的方法将绝缘材料覆盖在各层金属之间。由于制造工艺中需要沉积技术在晶圆上重复堆叠薄膜,因此薄膜沉积技术可视为前道工序中的“加法工艺”。

随着集成电路的发展,晶圆制造工艺不断精细化,芯片结构的复杂度也在不断提高,需要在更微小的线宽上制造。制造商要求制备的薄膜品种也随之增加,对薄膜性能的要求也在日益提高。

薄膜沉积的分类

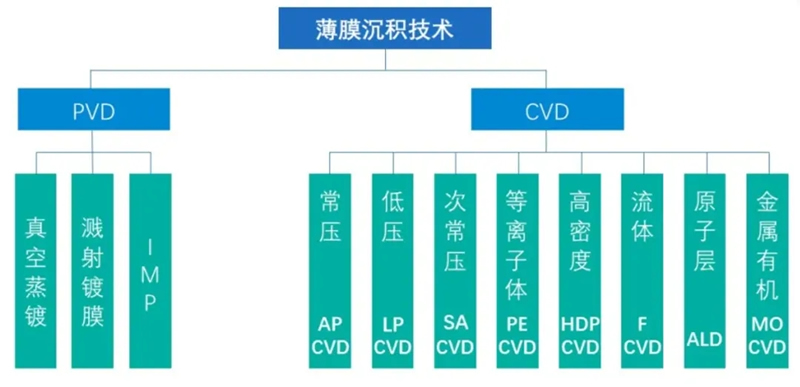

根据工作原理不同,薄膜沉积通常分为物理气相沉积(PVD)和化学气相沉积(CVD)。随着薄膜沉积工艺不断的发展,根据不同应用演化出了多种沉积设备用于晶圆制造的不同工艺。

这些技术各有所长,其中 PVD 主要应用于金属涂层的制备。CVD 主要应用于各种氮化物、碳化物、氧化物、硼化物、硅化物涂层的制备。原子层沉积(ALD) 属于新兴领域,一般用于 45nm 以下工艺中芯片的制备,具备良好的膜厚均匀性,同时在高深宽比的器件制备方面更具优势。

CVD 分类及应用

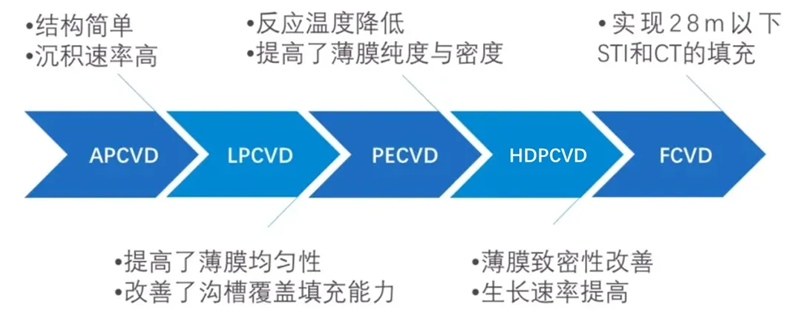

CVD 工作原理是,在真空高温条件下将两种以上气态或液态反应剂蒸汽引入反应室,在晶圆表面发生化学反应,形成一种新的材料并沉积。目前 CVD 市场占比最高且仍在不断迭代。

常压化学气相沉积(AP-CVD),是指在大气压及 400~800℃ 下温度进行反应,用于制备单晶硅、多晶硅、二氧化硅、掺杂 SiO2 等薄膜。

低压化学气相沉积(LP-CVD),是指用于90nm以上工艺中 SiO2 和 PSG/BPSG、氮氧化硅、多晶硅、Si3N4 等薄膜制备。

等离子增强化学气相沉积(PE-CVD),是用于 28~90nm 工艺中沉积介质绝缘层和半导体材料的主流工艺设备。其优点是沉积温度更低、薄膜纯度和密度更高,沉积速率更快,适用于大多数主流介质薄膜。相比传统的 AP-CVD、LP-CVD 设备,PE-CVD 设备已成为芯片制造薄膜沉积工艺中运用最广泛的设备类型。

沟槽填充类 CVD 设备,主要包括SA(次常压)-CVD、HDP(高密度等离子)-CVD、F(流体)-CVD 等设备,专门用于沟槽、孔洞处薄膜的填充。

SA-CVD 填孔能力很好;HDP-CVD 能够自下而上填充沟槽和孔隙,薄膜致密性更高,杂质含量更低;F-CVD 适用于 14nm 及以下工艺中细小沟槽的无缝隙填充。

尤其是 HDP-CVD,作为 PE-CVD 的一种特殊类型,其高密度等离子体中的原子/分子离子具有较高能量,在向衬底移动时轰击作用更强,从而引发溅射,可有效消除薄膜沉积过程中形成的悬垂结构,实现对沟槽及孔隙自下而上的填充。HDP-CVD 所制备的二氧化硅薄膜更致密,被广泛用于 45~130nm 工艺中 CMOS 集成电路的浅槽隔离(STI)填充。

ALD 用于沉积低 k 材料等介质时,无需加热,对器件损伤小;加热后 ALD 沉积速率较快,薄膜致密性好,但高温可能损伤薄膜,主要用于沉积金属栅极/高 k 金属化合物薄膜。

外延(EPI)设备,通常分为气相外延和分子束外延设备,既可以在硅衬底上沉积纯度更高、氧/碳缺陷密度更低的外延层,也可以在高掺杂硅衬底上生长外延层,有助于减小接触电阻,提高芯片运行速度。

金属有机化学气相沉积(MO-CVD)设备主要用于光电子、微电子器件等 GaAs、GaN、ZnSe 单晶材料的制备,优点是适用范围广,可生长多种化合物及异质结构材料。

三、“多才多艺”――离子注入

在集成电路制造过程中,要想使纯净硅具有可控的导电能力,就必须加入少量杂质使其结构和电导率发生改变,这一过程被称为掺杂,也是半导体注入灵魂的关键环节。

掺杂的工作可不是靠着能工巧匠们的手艺来完成的,它需要一套专门的、高度复杂的系统设备――离子注入机。

离子注入机通过对注入剂量、注入角度、注入深度、工艺温度等方面进行精确地控制,配合适当的掩膜材料,能够在晶圆区域上特定位置注入离子,就像一把高精度狙击步枪,可以精准命中目标,因此成为集成电路制造工艺中必不可少的关键装备。

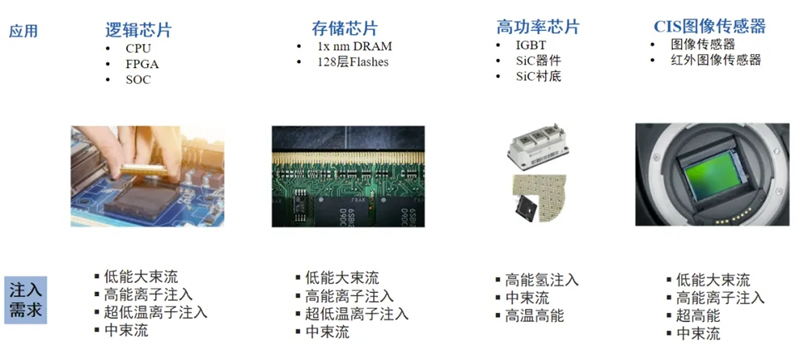

离子注入应用领域

离子注入应用非常广泛,不仅可用做大规模集成电路和器件以及半导体材料的掺杂,还能用于金属材料表面改性和制膜等方面。

从应用场景看,低能大束流离子注入机大规模应用于逻辑芯片、存储芯片和CIS芯片制造中。高能离子注入机较多应用在功率器件、IGBT、5G射频、CIS等器件制备过程中。

从产品类型来看,超低温低能大束流离子注入机和高能离子注入机均是集成电路制造装备产业链上“皇冠上的明珠”。负 100℃ 超低温离子注入是 FinFET 及更先进逻辑芯片制造中不可缺少的标准工艺。超低温注入特殊元素将晶硅材料预非晶化之后再进行离子注入掺杂和退火,从而减少晶体缺陷、降低漏电流,提高晶体管性能。

高能离子注入机,是离子注入机中技术难度最大的机型之一,更是国产 IGBT 产业加速追赶的关键之一。IGBT 俗称电力电子装置的“CPU”,在轨道交通、智能电网、航空航天、电动汽车与新能源装备等领域应用极广。自第三代 IGBT 技术诞生以来,IGBT 便与离子注入机结下了不解之缘。IGBT 芯片制备过程中采用离子注入技术进行器件正面和背面不同区域的掺杂。目前,IGBT 从 8 寸到 12 寸的关键之一就是背面高能离子注入(氢离子注入),该设备的单价也较高。

离子注入基本原理

众所周知,导体的基本条件是,材料内部要有足够多的自由电子作为导电介质。硅原子外层虽然有四个电子,但相对稳定性较强,流动性和自由度都很低,因此单晶硅的导电性很差。为改善导电性,需要向硅晶体中注入“杂质”以取代原有的硅原子的位置以增加自由电子的数量。

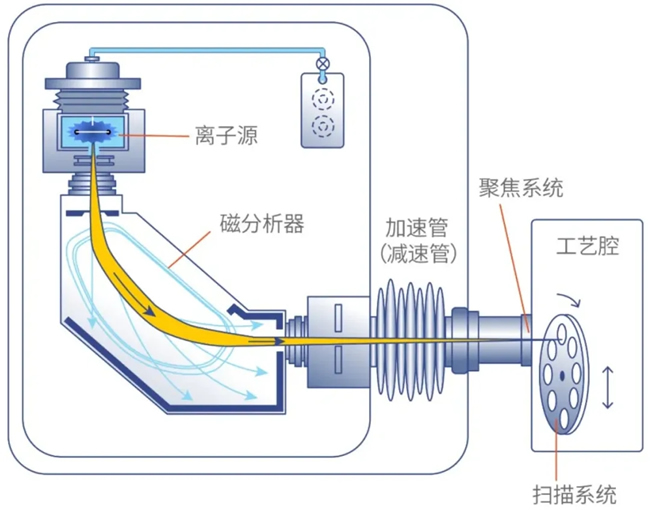

离子注入机通常由五部分组成,包括:离子源、质量分析器、加速管、扫描装置和工艺腔。离子注入的“杂质”可不是普通的物质,而是高纯度的硼、磷、砷等离子。常用的杂质源有 BF3、PH3、AsH3 等气体,离子源对这些高纯度的气体进行电离便可以得到等离子体。

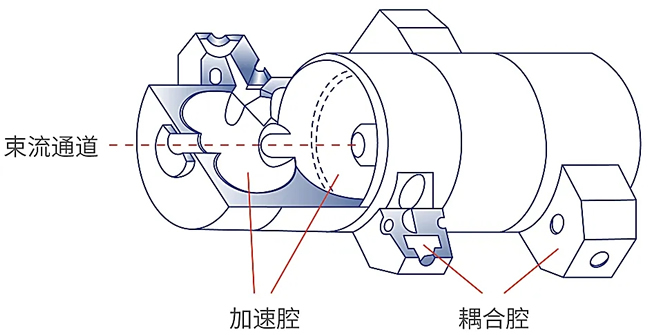

质量分析器通过调节内部的磁场强度对通过等离子体电离出的离子束进行偏转,质量过轻和过重的离子均被拦下来,只有一部分适合注入的离子能够通过分离孔。此外,要想实现“注入”,必须使离子具有很高的动能,才能穿透硅片表面到达特定深度,加速管的作用就是为离子“赋能”。

加速管内部会提供一个接近真空的环境,其中内置的多层电极会产生高压静电场,对通过其中的离子束加速。离子束每通过一层电极,就会获得更多的能量,离子的动能逐层累积加,最终会高达 50~200KeV。

离子束长时间轰击硅片上的一点会使其局部过热,造成不可恢复的损伤。为了避免该问题,需要利用扫描系统,在离子束与腔室中固定硅片在注入的过程中形成相对运动,使离子束均匀地注入其中。

常用的扫描方式有机械式、电磁式和混合式。机械式扫描是采用移动硅片的方法,通过移动工作室内的靶盘带动硅片运动。电磁式扫描是用则通过调整电磁场的强度将离子束偏转实现扫描,混合式则是将上述两种方式相结合。

以上,离子注入机的工作便宣告完成,可以得到了一片已经被注入了杂质离子的硅晶圆。不过距离完工还差最后一道工序――退火。由于短时间内涌入了那么多“外援”,硅晶体的内部其实已经非常杂乱,大量的杂质并没有按照要求站到合适的位置上,而是停在了硅原子间的空隙中,这不但没有达到实现掺杂的目的,反而挤乱了硅晶体原有整齐的结构,破坏了晶体稳定的结构造成了“注入损伤”。

为了消除注入损伤,需要在大约 1000℃ 的温度下对晶圆进行退火处理。高温所带来的动能可以使位置错乱的杂质原子获得很高的动能,并以较高的迁移率从而在晶体中移动,从间隙中回到正确的位置,让硅晶体的队伍结构再度整齐排列起来。

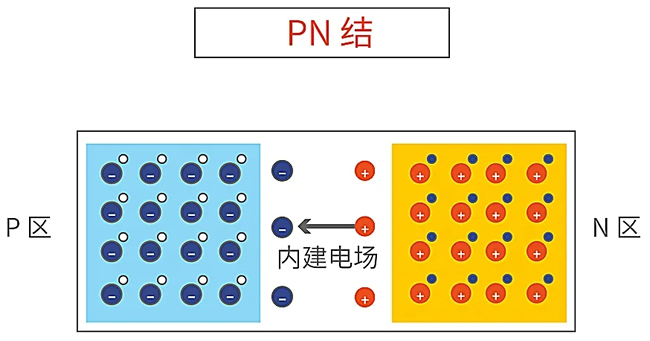

至此,离子注入工艺才宣告完成。在微观局部,掺杂后的杂质原子外层形成了带负电的 N 型(Negative)半导体,以及带正电的 P 型(Positive)半导体,P 型与 N 型的交合界面便是 PN 结,它具有单向导电的性质,就是这些微小的晶体管,作为开关可以调节两端电流的通断,从而实现复杂的逻辑计算。

素材来源官方媒体/网络新闻

|